...

19.1 Introduction

MIPI CSI (Camera Serial Interface) is a specification defined by MIPI (Mobile Industry Processor Interface) for connecting a camera and a CPU to transmit video signals from a camera. SP7021 supports CSI-2 specification which was released in 2005, using D-PHY as the physical layer. The main features list as below.

...

SP7021 supports two MIPI CSI-RX modules, the control registers locate at RGST Table Group 165~168 which memory map address are 9c005280h~9c00547fh.

Although the below descriptions focus on MIPI CSI0 module, but the MIPI CSI1 has the same structure.

...

19.2 Function Diagram

...

19.2.1 MIPI CSI connection

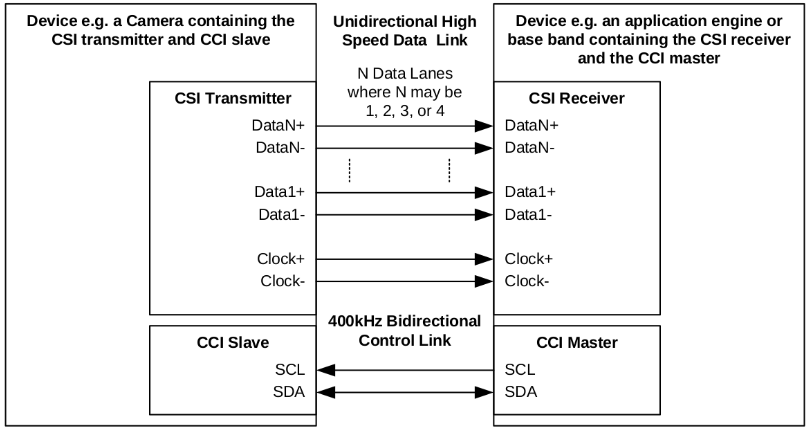

Figure 1819-1 shows the generic MIPI CSI pins connection.

Figure 1819-1 MIPI CSI Connection

- CCI (Camera Control Interface) is a two-way connection and is compatible with the I2C protocol. This interface is mainly used to access the registers in the camera to configure and control them. The host's I2C host controller is usually used, and the camera is used as the I2C slave device. The camera register layout and field definitions of different manufacturers are different.

- The CSI interface is a one-way transmission, which consists of a clock lane and one to four data lanes to transmit image data. Adopt D-PHY physical layer protocol.

...

19.2.2 MIPI CSI RX Block

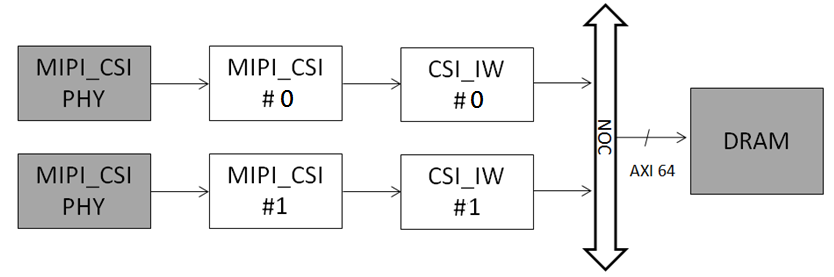

A generalized function diagram of MIPI CSI of SP7021 is shown in Figure 1819-2.

Figure 1819-2 MIPI CSI Functional Blocks

- MIPI-CSI PHY: The DPHY supports forward direction HS/LP transaction and reverse direction LP transaction.

- MIPI-CSI: MIPI-CSI receive data from DPHY and decode data (unpacks formats and byte to pixel).

- CSI-IW: Receive data from MIPI-CSI and store into DRAM.

...

19.3 DPHY Protocol

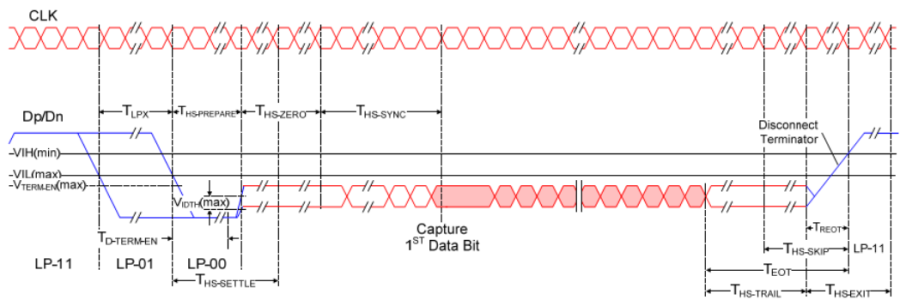

Figure 1819-3 shows the data transfer behavior between DPHYTX and DPHYRX which is described in DPHY SPEC.

Figure 1819-3 DPHY Protocol

In the part where the DP/DN is blue, it belongs to Low Power Mode, and the behavior on the interface is Large Voltage Swing. The part where the DP/DN is red line belongs to High Speed Mode, and the behavior on the interface is Low Voltage Swing. When you want to start transferring data, you will enter High Speed Mode from Low Power Mode. The behaviors will be in Low Power Mode with the voltage change from LP-11 -> LP-01 -> LP-00. After entering High Speed Mode, a series of HS-0 will be transmitted as the buffer between conversions. The followed HS-Sync pattern with data transmission is the valid data transmission

...

19.4 DPHY Operation with MIPI CSI

To start the entire MIPI System, firstly open the DPHY Low Power Mode Enable bit to transmit the lane (G165.6 mipi_analog_cfg2 register bit4). MIPI CSI will use Power Status Signal to determine when to enter High Speed Mode (basically by 1->0). Once you want to enter High Speed Mode, it will delay for a period of time (such as T-HS-SETTLE in Figure 1819-2, controlled by G165.9 mipicsi_delay_ctl register bit[15:8]) and then pull up HS Mode Enable to notify DPHY. On the other hand, if you enter Low Power Mode, MIPI CSI will lower HS Mode Enable.

When data transmission is performed on the data lane, the HS-SETTLE and HS-SYNC signals are sent first, then the data payload is sent, and finally ends with EOT (end of transmission), which is a complete physical layer packet.

...

19.5 MIPI CSI Protocol

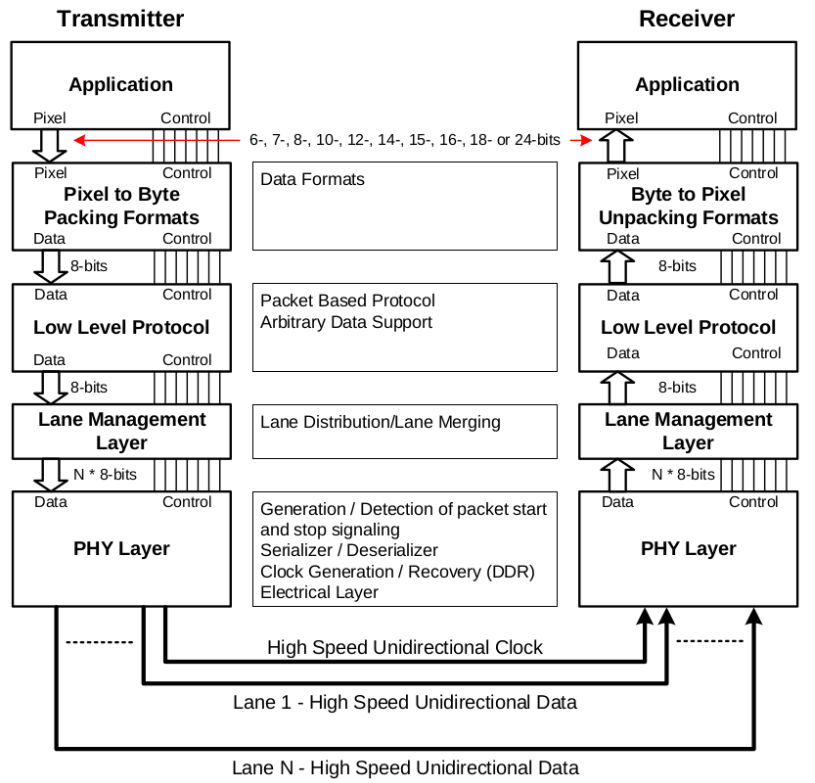

The MIPI CSI protocol include 3 layers, they are Pixel/Byte with Packing/Unpacking layer, Low Level Protocol layer and Lane Management layer. The protocol structure shows in figure 1819-4.

Figure 1819-4 MIPI CSI Protocol

...

19.5.1 Pixel/Byte with Packing/Unpacking Layer

In this layer, the transmitting end receives the pixel data from the application layer and packages it into a byte format for transmission to the next layer; at the receiving end, unpacks the data from the LLP (Low Level Protocol) layer and transmits it to the application layer.The main purpose of this layer is to convert different pixel formats (such as YUYV, RGBA, etc.) into 8-bit format, eliminating differences in different image formats and reducing transmission complexity.

...

19.5.2 Low Level Protocol Layer

The Low Level Protocol (LLP) layer is the main functional layer of the CSI protocol. It not only defines the packet format, but also defines the synchronization mechanism used in the transmission.

At the transmitting end, the layer is responsible for packing the data transmitted from the upper layer, adding a check field, adding the synchronization packet, and transmitting to the next layer; At the receiving end, the integrity of the packet is first verified, and each field is parsed, and the corresponding operation is performed according to the packet type, and the image data is transmitted to the upper layer.

The LLP processed payload data is converted pure byte data, and there is no pixel concept. The transmission of image data of one frame and one frame is realized by defining different fields and packet types.

...

19.5.3 Lane Management Layer

MIPI CSI-2 can be extended with data lane based on performance requirements. The number of data lanes can be one, two, three or four for different bandwidth requirements. The sender automatically distributes the data to each lane for transmission according to the number of lanes used; at the receiving end, the data on each lane is re-merged to recover the data.

This layer treats the packet transmitted by the LLP as a piece of pure byte data, and distributes it according to the number of lanes, regardless of the meaning of the data in the packet.

...

19.6 Registers Map

...

19.6.1 Registers Memory Map

Address | Group No. | Register Name | Description |

|---|---|---|---|

0x9C005380 | G167.0 | mipicsi status | MIPICSI key signal status |

0x9C005384 | G167.1 | mipi_debug0 | MIPICSI debug 0 |

0x9C005388 | G167.2 | mipi_wc_lpf | MIPICSI word count and analog LPF |

0x9C00538C | G167.3 | mipi_analog_cfg0 | MIPICSI analog config register 0 |

0x9C005390 | G167.4 | mipi_analog_cfg1 | MIPICSI analog config register 1 |

0x9C005394 | G167.5 | mipicsi_fsm_rst | MIPICSI FSM reset |

0x9C005398 | G167.6 | mipi_analog_cfg2 | MIPICSI analog config register 2 |

0x9C00539C | G167.7 | mipicsi_enable | Enable MIPICSI |

0x9C0053A0 | G167.8 | mipicsi_mix_cfg | MIPICSI digital and analog config register |

0x9C0053A4 | G167.9 | mipicsi_delay_ctl | Signal Delay Setting |

0x9C0053A8 | G167.10 | mipicsi_packet_size | Long packet size and number config |

0x9C0053AC | G167.11 | mipicsi_sot_syncword | SOT sync word |

0x9C0053B0 | G167.12 | mipicsi_sof_sol_syncword | SOF, SOL sync word |

0x9C0053B4 | G167.13 | mipicsi_eof_eol_syncword | EOF, EOL sync word |

0x9C0053B8 | G167.14 | mipicsi reserved a14 | Reserved |

0x9C0053BC | G167.15 | mipicsi reserved a15 | Reserved |

0x9C0053C0 | G167.16 | mipicsi_ecc_error | ECC error status |

0x9C0053C4 | G167.17 | mipicsi_crc_error | CRC error status |

0x9C0053C8 | G167.18 | mipicsi_ecc_cfg | ECC config |

0x9C0053CC | G167.19 | mipi_analog_cfg3 | MIPICSI analog config register 3 |

0x9C0053DC | G167.20 | mipi_analog_cfg4 | MIPICSI analog config register 4 |

...

Address | Group No. | Register Name | Description |

|---|---|---|---|

0x9C005400 | G168.0 | csiiw latch mode | CSIIW latch mode |

0x9C005404 | G168.1 | csiiw config0 | CSIIW config register 0 |

0x9C005408 | G168.2 | csiiw base addr | CSIIW base address |

0x9C00540C | G168.3 | csiiw stride | CSIIW line stride |

0x9C005410 | G168.4 | csiiw frame size | CSIIW frame size |

0x9C005414 | G168.5 | csiiw frmae buf | CSIIW frame buffer rorate |

0x9C005418 | G168.6 | csiiw config1 | CSIIW config register 1 |

0x9C00541C | G168.7 | csiiw frame size ro | CSIIW frame size of HW automatic detection |

...

19.6.2 Registers Description

| Anchor | ||||

|---|---|---|---|---|

|

RGST Table Group 165 MIPI CSI DePacket : MIPICSI0

165.0 MIPICSI key signal status (mipicsi status)

Address:0x9C005280

Reset:0x0

...